The SIRIUS core (acronym for Small Imprint RISC for Ubiquitous Systems) stands in performance somewhere between the very successful architectures of the ATMEL AVR (ATmega 8bit) , the TI MSP 430, the PicoBlaze – and well below the ARM 7/9– class of 32bit machines, the LEON (SPARC), Motorola 68xxx and other 32bit architectures (NIOS II, MicroBlaze). Although benchmarking still has to be done, the goals are easy to summarize:

- Load-Store architecture with 16bit external data bus.

- RISC architecture with 3 stage pipeline and 1 Instruction/clock cycle and an average of 0.8 MIPS/MHz performance.

- 16bit/32bit internal bus structure with 32bit ALU and 16×16 MPY,

- Orthogonal register set of 16 registers, 12 x16bit, 4 x 32bit, the 16bit universal registers may be combined to double registers and handled as 6 x32bit registers.

- Instruction pointer 32bit and stack pointer 32bit are part of the register set.

- Stack oriented architecture with unlimited nesting levels.

- Pointers 16 bit as well as 32bit supported.

- Multiplex bus system, separated 8bit IO bus and fast memory bus, all IO is connected via a separate 8bit bus with own address space

- Address space 64k or 4G depending on pointer addressing,

- Vectored hardware interrupt and software interrupt (exception)

- Compact 16 bit instruction format with only three modes

- Instruction set architecture with 56 instructions optimized for compact C-Compilation

- Netlist version made from gate primitives, able to be mapped on every existing technology without using macros.

- Performance about 300 MIPS in 0.13µm CMOS and 50 MIPS in actual FPGA-technologies

- Fully static, extreme low power design, all registers made from flip-flops.

- Comes with Software IDE, C-Compiler and Simulator and basic BIOS.

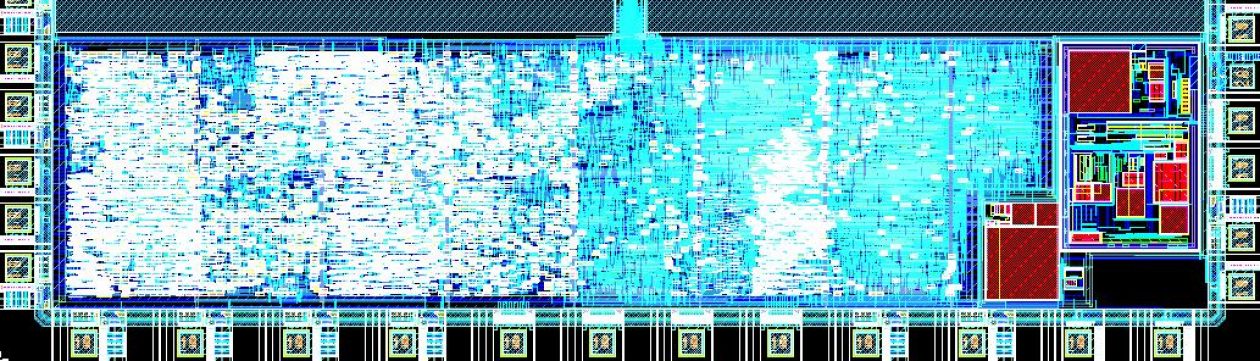

In the basic JANUS -version, a J. v. Neumann architecture with common program/data memory and 16bit bus is used, but also Harvard architecture with separate data RAM and program ROM is possible (SIRIUS-HULK) with small additional effort. This second version will come in form of a cache based memory model with separate Instruction and Data memory and will give true 1 Instruction/Cycle performance. Fig 1 shows a block diagram of the core.

One of the main ideas was to create a scalable, with requirements growing architecture, which can be fitted to every application from basic one chip designs, containing everything, up to OS- based designs with addressing capability of hundreds of Megabytes, using external DRAM and forming a complete Linux based system.

The design is further optimized for setting up a virtual machine for JAVA processing.

Any NOPs and any limitations in using instructions are avoided, allowing still assembler programming where it makes sense.

The goal of the SIRIUS development is a core with similar or improved features than the existing 16bit class of processors, but with better programmability and a high efficient C-Compiler for comfortable programming. A performance lower than the 32bit class is expected and accepted, for small memory imprint, an J. v. Neumann architecture is defined. Beside there are no caches, a good real time behavior is expected with several vectored interrupts. Most of all instructions run in 1 cycle with a 3 phase pipeline structure. There is a 32bit infrastructure for internal data handling and ALU processing, so that 32bit performance is not worse than 16bit performance, beside loads and stores need additional cycles. The instruction set is kept as small as possible, strongly related to the requirement of the compiler with a nearly one to one replacement of the DAG-operators by assembly instructions. Instructions for 32bit and 16bit are using the same mnemonics, so there are only few codes to remember.